Notice

Recent Posts

Recent Comments

Link

| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | ||

| 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| 13 | 14 | 15 | 16 | 17 | 18 | 19 |

| 20 | 21 | 22 | 23 | 24 | 25 | 26 |

| 27 | 28 | 29 | 30 |

Tags

- 아두이노

- 메타마스크

- 던전앤파이터

- MuchineRunning

- 컴퓨터구조

- 암호화

- 네트워크보안

- memory

- 반도체 취업

- 게임기획

- 아두이노함수

- 레지스터

- 아두이노우노

- 유니티에러

- 메모리

- 머신러닝

- 에러

- 반도체 엔지니어

- 인터럽트

- 유니티

- 네트워크

- MLAgent

- Unity

- 네오플

- 보안

- 이더리움

- neople

- 면접

- 던파

- 반도체

Archives

- Today

- Total

Dreaming Deve1oper

Integer Arithmetic / 정수 산술 연산 (Day 2) 본문

Half Adder

| A | B | C out | S |

| 0 | 0 | 0 | .0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Full Adder

| A | B | C in | S | C out |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

Subtraction = 2's Complemetnt + Addition

5-7

= 0101 - 0111

= 0101 + (-0111)

= 0101 + 1001

= 1110

= -2

→ 2's Complement를 취하면 음수로 바뀌기 때문.

Integer Arithmetic: Addition/Subraction

VZSC = Flag라고함.

- V: Overflow Flag

- Z: Zero Flag

- S: Sign Flag

- C: Carry Flag

→ Overflow가 발생하면 1Bit만 저장 가능하다. 발생할 경우 플래그를 1로 세팅. S가 음수가 될 경우 1로 세팅. Carry가 발생하면 1로 세팅.

→ Flag (플래그)들을 모아놓은것을 Status Register라고 함.

→ Carry Bit 표현: 최종적으로 상위비트에서 차상위비트로 올라가는 Carry가 있는지 확인하고 그대로 세팅.

→ Sign Bit 표현: 최상위 비트(msb) 를 본다. 0이면 양수, 1이면 음수이다. 1일 경우 sign이 1로 세팅됨. S1 ~ S4까지 4개의 결과가 모두 0일경우 zero flag가 1로 세팅되어야하기 때문에 or 후에 not을 취한다. (=nor/모두 0일 경우만 출력값이 1이 된다.)

→ Overflow: msb에서 올라오는 carry와 바로 밑에서 올라오는 (C4, C5)것을 XOR해서 저장한다.

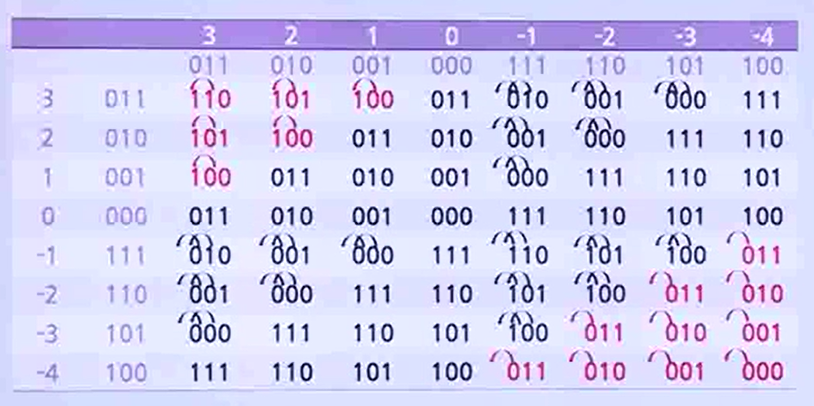

Integer Arithmetic: Overflow/Underflow

- 부호가 바뀌는지 판단하면 된다.

'컴퓨터 구조' 카테고리의 다른 글

| ALU: Arithmetic Operations (0) | 2022.03.20 |

|---|---|

| 부동 소수점 (BFPN) (0) | 2022.03.20 |

| 로직 연산 (Day 2) (0) | 2022.03.19 |

| ALU 아키텍처 / Integer 표현 (Day 2) (0) | 2022.03.19 |

| 반도체와 시스템의 발전 (Day 1) (0) | 2022.03.13 |

Comments