Notice

Recent Posts

Recent Comments

Link

| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | ||

| 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| 13 | 14 | 15 | 16 | 17 | 18 | 19 |

| 20 | 21 | 22 | 23 | 24 | 25 | 26 |

| 27 | 28 | 29 | 30 |

Tags

- 반도체 엔지니어

- 이더리움

- 던파

- 암호화

- 네트워크

- MuchineRunning

- memory

- 네트워크보안

- 머신러닝

- 인터럽트

- 유니티

- neople

- 에러

- 반도체 취업

- 게임기획

- 아두이노우노

- 메모리

- 네오플

- Unity

- 반도체

- 면접

- 메타마스크

- 컴퓨터구조

- 유니티에러

- 아두이노

- 레지스터

- 아두이노함수

- 던전앤파이터

- MLAgent

- 보안

Archives

- Today

- Total

Dreaming Deve1oper

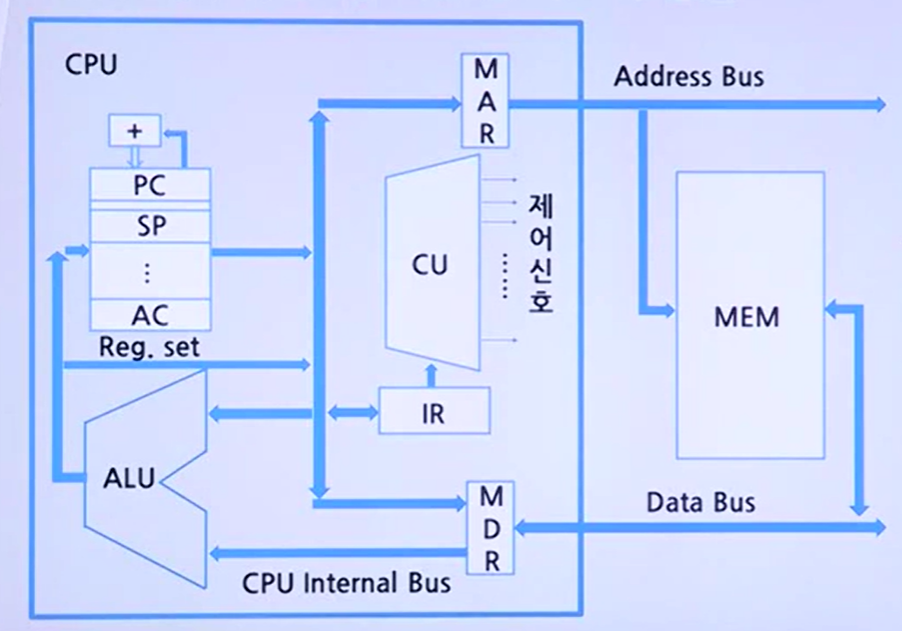

CPU의 구조와 구성 요소 본문

산술논리연산장치 (Arithmetic and Logic Unit: ALU)

- 산술 및 논리 데이터의 실질적인 연산을 위한 하드웨어 모듈.

- 산술연산: 사칙연산 ( +, -, *, / )

- 논리연산: 논리연산 ( AND, OR, NOT, XOR 등.. . )

레지스터 세트 (Register Set)

- CPU 내부의 다양한 레지스터들의 집합.

- 액세스 속도가 가장 빠르다 (CPU 내부에서 처리되기 때문)

- 제한적이다. (=CPU라는 한정된 면적안에 메모리를 넣어야하기 때문에 그 수가 제한적이다.)

| 특수기능레지스터(SPR) | 범용레지스터(GPR) |

| Program Counter (PC) | |

| Accumulator (AC) | |

| Instruction Register (IR) | |

| Memory Address Register (MAR) | |

| Memory Data Register (MDR) |

- Program Counter: 메모리의 주소정보를 가지고 있으며 자동으로 증가하는 역할을 수행하는 레지스터.

- Accumulator: 메모리에서 데이터를 가져올 때 어디에 먼저 저장할지 결정하는 레지스터.

- Instruction Register: Instruction을 가져왔을때 그것을 보관하는 레지스터.

- Memory Address Register: CPU에서 메모리와 연결될때 출입문 역할을 수행.

- Memory Data Register: CPU에서 메모리와 연결될때 출입문 역할을 수행.

- 범용레지스터: 메모리에서 CPU로 내용을 가져올때 어디에 두고 사용할것인지 관리하는 레지스터.

※ 레지스터가 16개일 경우 R0~R15까지 16개 사용 가능.

제어유닛 (Control Unit)

- CPU의 두뇌역할.

- 명령어의 연산코드(OP Code)를 해독하는 명령어 해독기.

- 해독에 따른 실행을 위한 제어신호들을 순차적으로 발생시키는 하드웨어 모듈.

- 마이크로 명령어들로 이루어진 마이크로 프로그램을 저장하는 제어기억장치 등으로 구성.

CPU 내부버스 (CPU Internal Bus)

- ALU와 레지스터들 간의 데이터 이동을 위한 데이터선들과 제어 유닛으로부터 발생되는 제어 신호 선들로 구성된 내부 버스.

- 외부의 시스템 버스들과는 직접적으로 연결되지 않고 반드시 버퍼 레지스터(MDR, MAR)들 혹은 시스템 버스 인터페이스 회로를 통하여 시스템 버스와 연결.

- Address Bus: MAR에서 나가는 것 / 단방향 / Unidirectional Bus

- Data Bus: MDR로 들어오는 것 / 양방향 / Bidirectional Bus

CPU 내부 레지스터: Program Counter (PC)

- 다음에 인출할 명령어 주소 값을 가지고 있는 레지스터. (메모리에 적재되어 있는 명령어들을 어떻게 순서대로 인출할 것인가)

- 각 명령어가 인출된 후에는 자동으로 일정 크기 (명령어 길이: 워드)만큼 증가한다.

- 분기 (Branch) 또는 조건 (Conditional) 명령어가 실행되는 경우에는 해당 명령어가 있는 목적지 주소 값으로 갱신된다.

CPU 내부 레지스터: Accumulator (AC)

- 처리할 데이터를 일시적으로 저장하는 레지스터.

- 레지스터의 크기: CPU가 한번에 처리할 수 있는 데이터 비트의 수 (워드의 길이)

CPU 내부 레지스터: Instruction Register (IR)

- 가장 최근에 지정된 주소 번지의 주기억장치로부터 CPU로 인출된 명령어 코드가 저장되는 레지스터. (=메모리에 있는 명령어가 올 때 IR로 간다)

CPU 내부 레지스터: Stackpointer Register (SP)

- 이미 메모리에 설정된 스택의 시작번지의 주소값을 가지고 있으며 스택에 정보가 쌓이거나 줄어드는 것에 따라 그의 값이 증가 혹은 감소하는 레지스터.

CPU 내부 레지스터: Memory Address Register (MAR)

- 다음에 인출될 명령어의 주소정보는 PC에 있고, 현재 CPU 내부로 불러올 명령어의 주소값을 메모리로 전달되기 전에 그것을 일시적으로 저장하는 레지스터.

CPU 내부 레지스터: Memory Data(=Buffer) Register (MDR)

- 주기억장치로부터 읽혀질 혹은 쓰여질 데이터를 일시적으로 저장하는 레지스터.

'컴퓨터 구조' 카테고리의 다른 글

| 명령어 주소 지정 방식 (0) | 2022.03.26 |

|---|---|

| 명렁어 세트 (0) | 2022.03.26 |

| ALU: Arithmetic Operations (0) | 2022.03.20 |

| 부동 소수점 (BFPN) (0) | 2022.03.20 |

| Integer Arithmetic / 정수 산술 연산 (Day 2) (0) | 2022.03.19 |

Comments